CXL 整理 (更新版)

CXL的类型分类、特性整理

本文内容全部来源于 Compute Express Link (CXL) Specification Revision 3.2, Version 1.0。笔者主要关注与 CXL 扩展内存池相关的内容,内容并不全面。

概览

CXL 是一种高性能 I/O 总线架构,用于连接外设,这些外设可以是传统的非一致性 I/O 设备、内存设备,或具备附加功能的加速器。

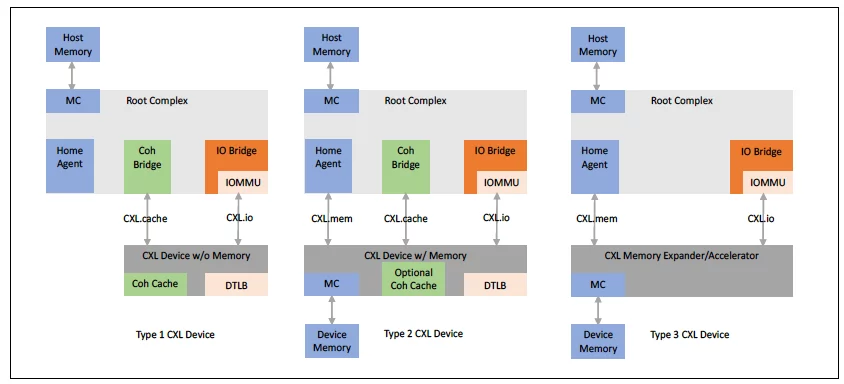

通过 CXL 连接的设备类型及整体系统架构如下图所示:

其中 Type2 和 Type3 型设备可以拥有向主机暴露的内存资源,这样的内存被称为 Host-managed Device Memory (HDM)。这种内存的一致性管理有三种选项:仅主机一致性(HDM-H)、设备一致性(HDM-D)以及使用反向失效嗅探的设备一致性(HDM-DB)。

CXL 设备通过三种协议与主机通信:

- CXL.io:基于 PCIe 协议,支持传统的非一致性 I/O 设备。

- CXL.cache:支持缓存一致性,适用于 Type1 和 Type2 型设备。

- CXL.mem:支持内存语义,适用于 Type2 和 Type3 型设备。

在下面的描述中,我们将分别介绍 CXL 的系统架构(3种类型的设备)和三种事务层协议(CXL.io、CXL.cache 和 CXL.mem)。以下的介绍可能相互交错(例如在介绍 CXL type2型设备时,无法避免会涉及一部分 CXL.cache 协议内容,请上下文对照阅读、综合理解)。这一点在 CXL specification 中也是如此,请读者谅解。

CXL 系统架构(本章介绍3种类型的设备)

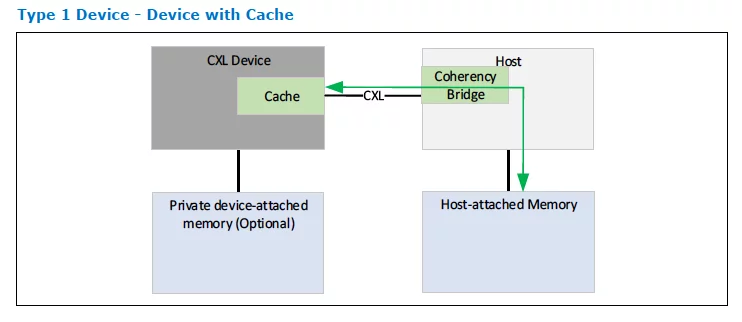

CXL type1 型设备

CXL type1 型设备是一个拥有本地缓存的加速器。它不包含任何主机可见的内存资源,因此不支持内存语义。Type1 型设备通过 CXL.io 协议与主机通信,并通过 CXL.cache 协议与主机内存进行缓存一致性交互。

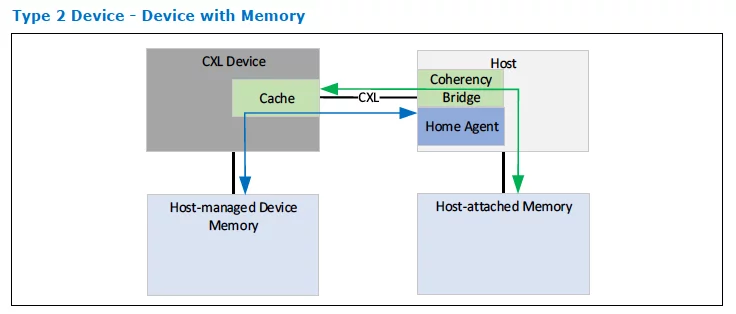

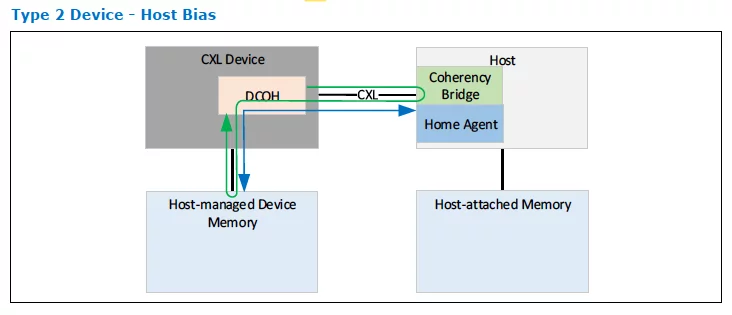

CXL type2 型设备

CXL type2 型设备是一个拥有本地缓存和主机可见内存资源的加速器。它在 Type1 型设备的基础上增加了对内存语义的支持,主机可以通过 CXL.mem 协议访问设备的内存资源。type2 型设备的主要目标是为主机提供一种方式,将操作数推送到设备挂载内存,并从设备挂载内存中拉取结果。

CXL type2 型设备需要向主机暴露自己的内存资源,同时本地的加速器也能够读写本地内存资源,因此需要维护缓存一致性。

主机CPU通过内存语义访问设备内存走的是 CXL.mem 协议,主机 CPU 与设备之间的缓存一致性维护可能走 CXL.cache 协议,也可能走 CXL.mem 协议,具体如下:

有两种方法维护主机与CXL设备之间的缓存一致性:

- 第一种方法使用 CXL.cache 来管理 HDM 的一致性,被称为“设备一致性”。支持此流程的内存区域以 “D” 作为后缀(HDM-D)。

- 第二种方法使用 CXL.mem 中的专用通道,反向失效嗅探(Back-Invalidate Snoop),以 “DB” 作为后缀(HDM-DB)。

备注:这里的一致性指的是 CXL 设备和主机都拥有 CPU 缓存,都可以访问 HDM,因此需要维护这两者之间的 CPU 缓存一致性。

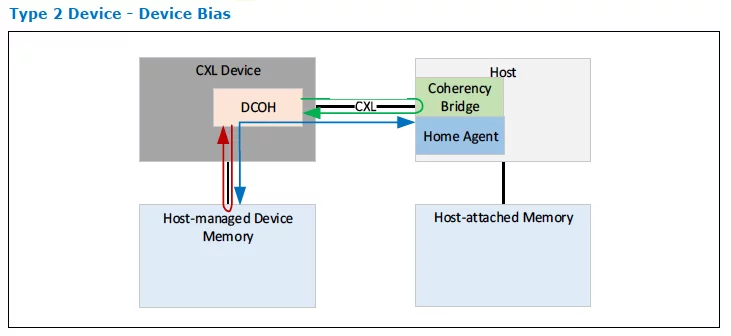

HDM-D

基于CXL.cache协议,使用基于偏向的模型(Bias-based Coherency Model)。简单来说有两种偏向:设备偏向和主机偏向。

设备偏向:

简单理解:设备可以快速读写内存,但是主机对内存的所有操作都需要发送到设备上,由设备代为处理。可以优化设备的内存访问性能。

主机偏向:

简单理解:主机可以快速读写内存,但是设备对内存的所有操作都需要发送到主机上,由主机代为处理。可以优化主机的内存访问性能。

补充:

软件辅助的偏向切换:一些设备支持按页粒度选择主机偏向或设备偏向模式,从而优化一致性性能。

硬件自主偏向模式管理:一些设备可以支持将内存页的访问模式检查卸载到加速器本身的硬件,由硬件控制页面粒度的偏向模式切换,或者由硬件向上层软件提供偏向模式建议。

备注:尽管上面两个基于偏向的模型都用来描述 HDM 内存(主机管理的设备内存),但是相似的内存一致性模型也可以用于 CXL 设备对于主机内存的访问。CXL 设备可以通过 CXL.cache 协议访问主机内存,并且可以使用类似的偏向模型来管理与主机之间的缓存一致性。例如当CXL设备访问主机内存时,为防止主机缓存中存在未刷新的数据,CXL设备可以向主机发送请求,请求主机刷新缓存和返回最新的数据。

HDM-DB

备注:HDM-DB 模式并不是 CXL type2 型设备独有的,CXL type3 型设备也可以支持 HDM-DB 模式。

HDM-DB 基于 CXL.mem 协议,使用反向失效嗅探(Back-Invalidate Snoop)机制来维护一致性。简单来说,主机和设备都可以直接访问 HDM-DB 内存区域,并且都可以缓存这些内存区域的数据。当主机或设备对 HDM-DB 内存区域进行写操作时,设备上的控制器会发送一个反向失效嗅探消息,通知对方使其缓存失效,从而保证一致性。

简单理解:CXL 设备上有一个管理缓存一致性的代理,这个代理维护着设备内存中每个缓存行的状态,知道哪些设备缓存了哪些缓存行。当主机或设备对 HDM-DB 内存区域进行写操作时,代理会发送一个反向失效嗅探消息,通知对方使其缓存失效,从而保证一致性。

备注:HDM-DB 模式只用于设备和主机以缓存一致的方式访问设备的内存,不包含设备对主机内存的访问。

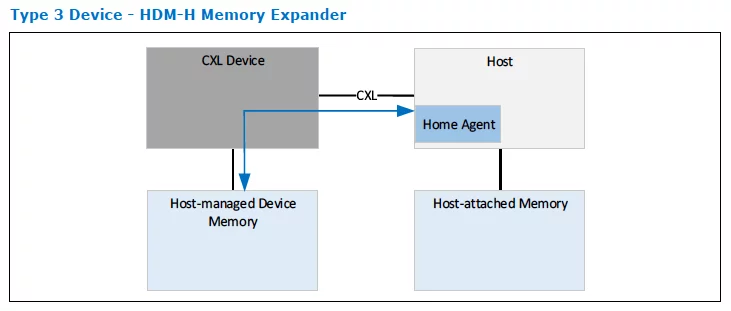

CXL type3 型设备

CXL type3 型设备是一个没有本地缓存但拥有主机可见内存资源的设备。简单理解可以是一种插在主机上的内存扩展卡。

CXL type3 型设备可能支持缓存一致性,也可以不支持。

不支持缓存一致性的 type3 型设备使用 HDM-H 方式向主机暴露内存,完全由主机来维护一致性。

支持缓存一致性的 type3 型设备扩展内存使用 HDM-DB 方式向主机暴露内存,使用 CXL.mem 协议中的反向失效嗅探机制来维护一致性。对于单台主机连接到单个 type3 型设备的场景,HDM-DB 维护的缓存一致性意义不大,以为设备完全没有缓存,主机也没有其他 CPU 缓存需要维护一致性。但是对于多主机连接到同一个 type3 型设备的场景(可能是通过CXL交换机,也可能是通过一个多插槽的内存扩展器),HDM-DB 维护的缓存一致性就非常有意义。

多逻辑设备:type3 型设备可能支持多逻辑功能,Multi Logical Device (MLD),可以把一个物理设备划分为多个逻辑设备,每个逻辑设备可以有独立的内存资源和配置空间,主要用于需要隔离的场景。

多头设备:type3 型设备可能支持多头功能,Multi-Head Device (MHD),可以把一个物理设备划分为多个头,每个头可以连接到不同的主机,每个头可以有独立的内存资源和配置空间,主要用于需要多主机访问的场景。一般呈现为一个内存扩展卡,存在多个插槽,每个插槽可以通过一根特殊的延长线插到一台独立的主机上,从而实现多主机访问同一个内存扩展卡。多个主机访问的扩展内存区域可以是共享的也可以是相互隔离的,具体取决于设备的设计和用户的配置。

多头设备和多逻辑设备可以结合使用,从而实现更复杂的场景,例如多头设备的每个头都包含多个不同的逻辑设备。

基于 CXL.type3 型设备的内存池

CXL type3 型设备可以用于构建内存池,从而为主机提供大容量、低延迟的内存资源。内存池可以通过 CXL 交换机或自身的多个接口连接到多个主机,从而实现内存资源的共享和动态分配。

注意,当多个主机连接到一个共享内存池时,需要考虑多主机之间的缓存一致性问题。

如果设备只支持软件缓存一致性(HDM-H),那么所有的缓存一致性维护工作都由主机来完成,设备不需要参与。这种情况下,主机需要确保对共享内存池的所有访问都是一致的。在这种情况下,多个主机之间的原子内存访问操作(例如c++ std::atomic)是无法通过硬件直接支持的。

请注意在仅支持软件缓存一致性的共享内存池当中,多主机之间的并发管理可能比基于 RDMA 的传统内存池更加复杂,因为 RDMA 至少支持硬件级别的原子读/写/FAA/CAS操作,而软件缓存一致的CXL内存池无法支持这些操作

共享内存池也可能支持硬件缓存一致性(HDM-DB),从而允许多个主机之间通过硬件维护缓存一致性。这种情况下,设备需要维护一个缓存一致性代理,代理维护着内存中每个缓存行的状态,知道哪些主机缓存了哪些缓存行。当主机对共享内存池进行读/写操作时,代理会发送一个反向失效嗅探消息,通知其他主机使其缓存失效,从而保证一致性。这样就可以支持多个主机之间的原子内存访问操作。

支持硬件一致性的共享内存池可以借助 CXL.mem 提供的特殊命令实现对特定缓存行的独占访问权限,因此支持任意的原子内存访问操作(例如c++ std::atomic)。这使得多主机之间的并发管理更加简单和高效。

因为维护缓存一致性的开销很高,受限于芯片面积和功耗等因素,一般认为 HDM-DB 内存区域的容量不会很大。实际可能在数百 MB 到数 GB 之间。预计将来的 CXL 扩展内存设备会有很大的 HDM-H 内存区域,和一个相对较小的 HDM-DB 内存区域。

_ 可以借助 HDM-DB 进行复杂的控制信息交换,而大部分数据存储在 HDM-H 内存区域。_

CXL 的三个事务层协议

CXL.io 协议

CXL.io 协议类似传统的 PCIe 协议,支持传统的非一致性 I/O 设备。CXL.io 协议使用 PCIe 的配置空间、内存空间和 I/O 空间来访问设备的寄存器和内存资源。CXL.io 协议还支持 PCIe 的中断机制。

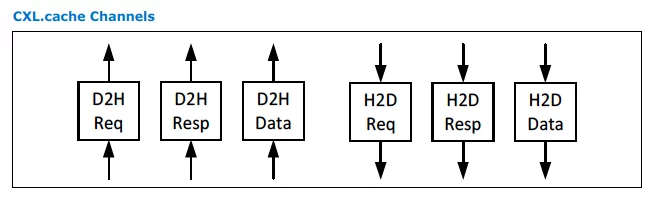

CXL.cache 协议

CXL.cache 协议提供主机到设备和设备到主机两个方向的数据通道,分别又分为请求、响应和数据三种。

这些数据通道用于发送缓存行读写/失效请求和响应,从而实现缓存一致性,在此基础上就能实现上面的设备偏向和主机偏向两种缓存一致性模型。本文省略具体的通道和命令定义,有兴趣的读者可以参考 CXL 规范。

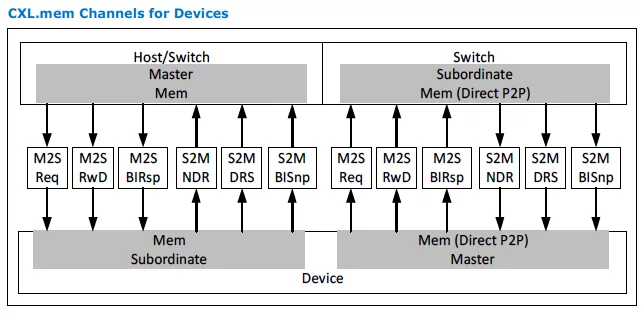

CXL.mem 协议

CXL.mem 协议允许主机以内存语义访问设备内存资源。部分设备支持反向失效嗅探(Back-Invalidate Snoop)机制来维护主机和设备之间的缓存一致性。

向主机暴露的设备内存资源被称为 Host-managed Device Memory (HDM)。可能有三种类型的 HDM:

- HDM-H:仅主机一致性(Host-only Coherency),完全由主机来维护一致性,不支持缓存一致性。

- HDM-D:设备一致性(Device Coherency),使用 CXL.cache 协议来维护一致性。这部分内容实际不属于 CXL.mem 协议范畴,在介绍 CXL.cache 协议时已经介绍过。

- HDM-DB:使用反向失效嗅探的设备一致性(Device Coherency with Back-Invalidate Snoop),使用 CXL.mem 协议中的反向失效嗅探机制来维护一致性。由设备维护一个缓存一致性代理,代理维护着内存中每个缓存行的状态,知道哪些设备缓存了哪些缓存行。当主机或设备对 HDM-DB 内存区域进行读/写操作时,代理会发送一个反向失效嗅探消息,通知对方使其缓存失效,从而保证一致性。因为维护缓存一致性的开销很高,受限于芯片面积和功耗等因素,一般认为 HDM-DB 内存区域的容量不会很大。实际可能在数百 MB 到数 GB 之间。预计将来的 CXL 扩展内存设备会有很大的 HDM-H 内存区域,和一个相对较小的 HDM-DB 内存区域。

CXL.mem 协议提供主机到设备和设备到主机两个方向的数据通道,分别又分为请求、响应和数据三种。CXL.mem 协议还为p2p(peer-to-peer)传输提供了专用的数据通道,从而允许设备之间直接传输数据,而无需经过主机CPU。

这些通道用于发送内存读写请求和响应,以及反向失效嗅探消息,从而实现内存语义访问和缓存一致性维护。本文省略具体的通道和命令定义,有兴趣的读者可以参考 CXL 规范。